# LETTER Low-power Adiabatic Logic Circuit: Simulation and Energy Dissipation Comparison

Nazrul ANUAR<sup>†a)</sup>,

**SUMMARY** This paper investigates the design approaches of low-power adiabatic logic gates in terms of energy dissipation associated with the input transition. A computer simulation using SPICE is carried out on several inverter circuits implemented using 0.18  $\mu$ m CMOS technology. Driving pulse with the height equal to  $V_{dd}$  is supplied to the logic gates. The dissipation characteristics are also compared at the different load capacitance values.

key words: adiabatic logic

### **Presentation content**

- $\bullet~2008/09/26$  : Circuit Simulation and Energy dissipation at different C

- 2008/10/03 : Circuit Simulation and Energy dissipation at different C (continue)

- 2008/10/10 : Circuit Simulation with new diagrams

- 2008/10/17 : More Circuit Simulation and Energy Dissipation comparison

- 2008/10/27 : Simulation using new MOS parameters and updated Energy Dissipation comparison

#### 1. Introduction

The development of CMOS technology provides high density and high performance to integrated circuits. As the density of an integrated circuit increases, the power consumption increases and its temperature control becomes difficult. Moreover, mobile devices require a high performance, light weight, and long operation time, which are contradictory characteristics. Adiabatic computing is an attractive approach in this viewpoint. In recent years, studies on adiabatic computing have been grown for low power systems and several adiabatic logic families have been proposed.

In this paper we examine the functional and energy dissipation of adiabatics circuits using computer simulation compared to conventional static CMOS logic circuit. Then we arrange them according to the total dissipated energy and other information such as the number of gates and driving pulse. We also simulate the effect of the load capacitance to the energy dissipation. 1.1 Adiabatic Logic Circuit Group

#### 1.1.1 Asymptotically Adiabatic Logic

In [1], asymptotically adiabatic logic comprised of circuits in which dissipation results solely from finite rate of change of driving voltage and can be decreased to any desired level. It is represented by 2n2p-2n logic [2] [3], 1n1p logic that is using the split-level driving pulses [4] and split-level charge-recovery logic [5].

1.1.2 Quasi-Adiabatic Logic

The second group of adiabatic logic is quasiadiabatic logic [1] which comprised of circuits which dissipation can be reduced appreciably by lowering the rate of change of driving voltage. It is divided into another 2 groups, which is the static approach and the dynamic approach.

The static is represented by 1n-1p [6] and 2n-2n2p quasi-adiabatic logic [7]. The dynamic approach is represented by Hot-Clock nMOS (HCnMOS) logic [8], Recovered-Energy logic (REL) [9] [10], Adiabatic Dynamic Logic (ADL) [11] [12], Efficient charge-recovery logic (ECRL) [13], Adiabatic Dynamic CMOS Logic (ADCL) [14] and 2-Phase Adiabatic Dynamic CMOS Logic (2PADCL) [15].

### 2. Simulation and Results

#### 2.1 Conditions

The paper starts by examining the functional and energy dissipation of a simple logic gate, an inverter. The simulations using LTSpice are carried out for all the circuits reviewed in [1]. Circuits are connected to the pulse driving voltage, $\phi$  and input signal according to the layouts. The operation clock frequency is 50 MHz. Length and width of the nMOS and pMOS logic gates used in this simulation are L=0.18  $\mu$ m, W=0.6  $\mu$ m.

The most suitable load capacitor value for each circuits is examined according to the output voltage waveforms. Circuits diagrams and simulation results in the form of waveforms are represented by Fig. 1 – Fig. **??**. The energy dissipation is calculated by integrating the

<sup>&</sup>lt;sup>†</sup>The author is with the Electronics and Information Systems Division, Graduate School of Engineering, Gifu University, 1-1 Yanagido Gifu-shi, Gifu 501-1193 Japan

a) E-mail: n3814101@edu.gifu-u.ac.jp

voltage and current product value as follows

$$E = \int_0^{T_s} \left( \sum_{i=1}^n (V_{pi} \times I_{pi}) \right) dt \tag{1}$$

where  $T_s$  is the period of the primary input signal,  $V_p$  is the power supply voltage,  $I_p$  is the power supply current and *i* is a number of power supply [2].

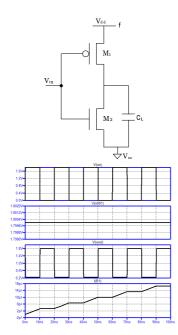

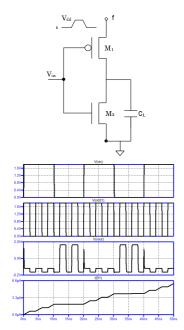

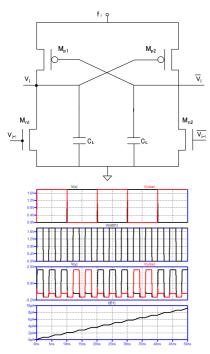

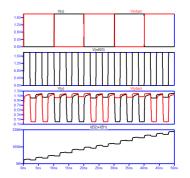

$\label{eq:Fig.1} {\bf Fig.1} \quad {\rm Conventional\ CMOS\ logic\ inverter\ circuits\ diagram\ and} \\ {\rm waveforms\ }$

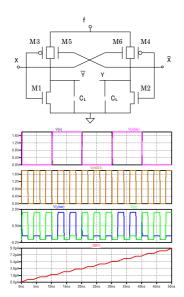

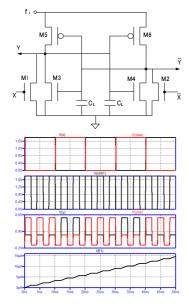

Fig. 2 2n2p-2n adiabatic logic inverter circuits diagram and waveforms

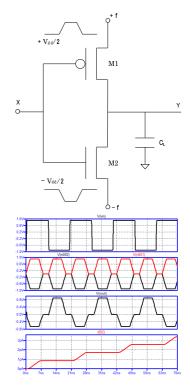

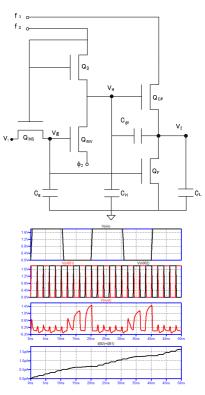

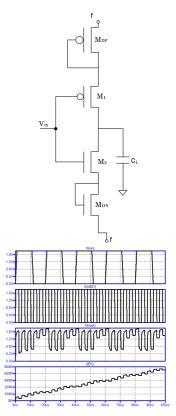

Fig. 3 Split level pulse 1n1p logic inverter circuits diagram and waveforms

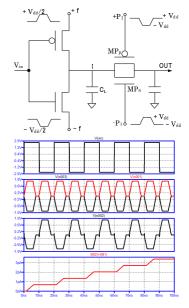

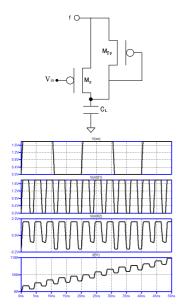

${\bf Fig.\,4}$   $\;$  Split level charge-recovery logic inverter circuits diagram and waveforms

#### 2.2 Circuits comparison

Table 1 lists the features of all logics in the review for comparison. In this preliminary results, ADL show the lowest value of energy dissipated per cycle while 2n-2n2p quasi adiabatic show the highest. 7 out of 10 adi-

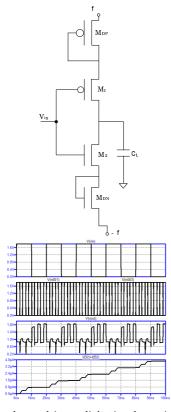

Fig. 5 1n-1p quasi-adiabatic logic inverter circuits diagram and waveforms

Fig. 6  $2n-2n^2p$  quasi-adiabatic logic inverter circuits diagram and waveforms

atic circuits show a lower energy dissipation compared to conventional static CMOS by reducing from 98% to 17%.

# 2.3 Energy dissipation at different load capacitance

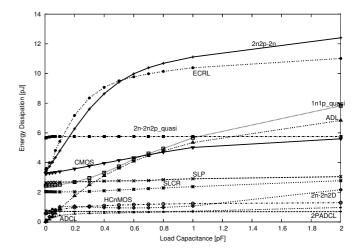

The simulation result on the energy dissipation at different load capacitance is shown in Fig. 14. As expected, all the circuits, except 2PADCL show an increase of dissipated energy when changing the load capacitor to a higher value.

Fig. 7 Hot-clock nMOS logic inverter circuits diagram and waveforms  $% \left( {{{\mathbf{F}}_{\mathrm{s}}}_{\mathrm{s}}} \right)$

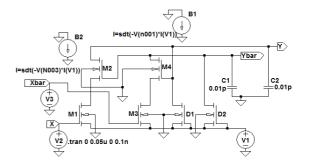

$\label{eq:Fig.8} {\bf Fig.8} \quad {\rm Recovered-energy \ logic \ (REL) \ in \ MOSFETs \ inverter \ circuits \ diagram \ and \ waveforms$

# 3. Discussion

- Analysis of the adiabatic circuits using LTSpice shown that the energy dissipation per cycle can be calculated and therefore is convinience for futher analysis and design. In this simulation result, ADL shows the lowest energy dissipation as an inverter

- Load Capacitance which use as the data holder need to be design precisely considering the time

Fig. 9 Adiabatic Dynamic logic (ADL) inverter circuits diagram and waveforms  $\$

$\label{eq:Fig.10} {\bf Fig. 10} \quad {\rm Efficient\ charge-recovery\ logic\ (ECRL)\ circuits\ diagram\ and\ waveforms$

constant that effect the output and also the amount of information to be stored

- Unlike other circuits 2PADCL shows a decrease in energy dissipation when the load capacitance increased. If this is true, this circuit has a higher possibility to be further studied

- REL in MOSFETs circuits are still not operating very well in this simulation. Further corrections need to be carried out.

Fig. 11 Modified Adiabatic Dynamic CMOS logic (ADCL) circuits diagram and waveforms

| Table 1 Comparison of Power Dissipatio | Table 1 | Comparison | of Power | Dissipation |

|----------------------------------------|---------|------------|----------|-------------|

|----------------------------------------|---------|------------|----------|-------------|

|                 | -                | -     |               |

|-----------------|------------------|-------|---------------|

| Adiabatic Logic | Energy(pJ/cycle) | Gates | Driving Pulse |

| ADL             | 0.035            | 4     | 4             |

| 2n-2n2d         | 0.116            | 6     | 1             |

| ADCL            | 0.133            | 4     | 1             |

| HCnMOS          | 0.60             | 5     | 2             |

| 1n-1p SLCR      | 0.68             | 4     | 1             |

| 2PADCL          | 0.77             | 4     | 2             |

| 1n-1p SLP       | 0.86             | 2     | 2             |

| 1n-1p quasi     | 2.04             | 2     | 1             |

| CMOS            | 3.00             | 2     | 1             |

| 2n2p-2n         | 3.45             | 6     | 1             |

| ECRL            | 3.61             | 4     | 1             |

| 2n-2n2p quasi   | 4.55             | 6     | 1             |

| REL (MOSFET)    | 5.74             | 4     | 1             |

|                 |                  |       |               |

### 4. Conclusion

We have done simulations to find out the functional and energy dissipation characteristic of each adiabatic logic circuits. We conclude that most of the proposed circuits have lower energy dissipation compared to conventional CMOS logic.

# 5. Next Plan

• Further analysis on ADL, ADCL, REL in MOS-FETs and 2N-2N2D adiabatic logic

Fig. 12 Two-phase drive adiabatic dynamic CMOS logic (2PADCL) circuits diagram and waveforms

#### References

- V.I Starosel'skii Adiabatic Logic Circuits: A Review, Russian Microelectronics, 2002, Vol.31, No. 1, pp.37-58

- [2] Athas, W.C., Svensson, L.J., Koller, J.G., Tzartzanis, N., and Chou, E.Y.-C., Low-Power Digital Systems Based on Adiabatic-Switching Principles, *IEEE Trans. VLSI Syst.*, 1994, vol. 2, no. 4, pp. 398?407.

- [3] Ferrary, A., Adiabatic Switching, Adiabatic Logic, Wed Mar 20 12:14:22 PST 1966.

- [4] Valiev, K.A. and Starosel skii, V.I., A Model and Properties of a Thermodynamically Reversible Logic Gate, *Mikroelektronika*, 2000, vol. 29, no. 2, pp. 83–98.

- [5] Younis, S.G. and Knight, T.F., Asymptotically Zero Energy Split-Level Charge Recovery Logic, Proc. 1994 Int. Workshop on Low Power Design, 1994, pp. 177–182.

- [6] Starosel škii, V.I., Reversible Logic, Mikroelektronika, 1999, vol. 28, no. 3, pp. 213–222.

- [7] Denker, J.S., A Review of Adiabatic Computing, Proc.1994 Symp. on Low Power Electronics, San Diego, 1994.

- [8] Seitz, C.L., Frey, A.H., Mattisson, S., Rabin, S.D., Speck, D.A., and van de Snepscheut, J.L.A., Hot-Clock nMOS, 1985 Chapel Hill Conference on Very Large Scale Integration, Fuchs, H., Ed., Rockville, Md.: Computer Science, 1985, pp. 1–17.

- [9] Himman, R.T. and Schlecht, M.F., Recovered Energy Logic: A Highly Efficient Alternative to Today 's Logic Circuits, Proc. IEEE Power Electron. Specialists Conf., 1993, pp. 17–26.

- [10] Himman, R.T. and Schlecht, M.F., Recovered Energy Logic: A Single Clock AC Logic, Proc. IWLPD '94 Work-

Fig. 13 2n-2n2D circuits diagram and waveforms

Fig. 14 Energy dissipation comparison in adiabatic circuits at different load capacitance value

shop, 1994, pp. 153-158.

- [11] Dickinson, A.G. and Denker, J.S., Adiabatic Dynamic Logic, Proc. IEEE 1994 CICC, pp. 282–285.

- [12] Dickinson, A.G. and Denker, J.S., Adiabatic Dynamic Logic, *IEEE J. Solid-State Circuits*, 1995, vol. 30, no. 3,pp. 311–315.

- [13] Moon, Y. and Jeong, D.-K., An Efficient Charge Recovery

Logic Circuit, IEEE J. Solid-State Circuits, 1996, vol. 31,

- no. 4, pp. 514–522. [14] K. Takahashi and M. Mizunuma, Adiabatic dynamic CMOS logic circuit, IEICE Trans. Electron. (Japanese Edition), vol. J81-CII, no. 10, pp. 810?817, Oct. 1998 (Electronics and Communications in Japan Part II (English Translation), vol. 83, no. 5 , pp. 50–58, April 2000).

- [15] Y. Takahashi, Y. Fukuta, T. Sekine, and M. Yokoyama, 2PADCL : Two Phase drive Adiabatic Dynamic CMOS Logic, Proc. IEEE APCCAS, Dec 2006, pp. 1486-1489